What is pipeline?

Pipelining attempts to keep every part of the processor busy with some instruction by dividing incoming instructions into a series of sequential steps (the eponymous “pipeline”) performed by different processor units with different parts of instructions processed in parallel.

MIPS is Designed for Pipeline

- ALl instruction is 32-bit

It means that easier to fetch instruction - Only 3 types of instruction format

Decode and read registers in one step - Load/store(or reg-reg) architecture

Can calculate address in an early stage, access memory in a late stage? - Alignment of memory operands

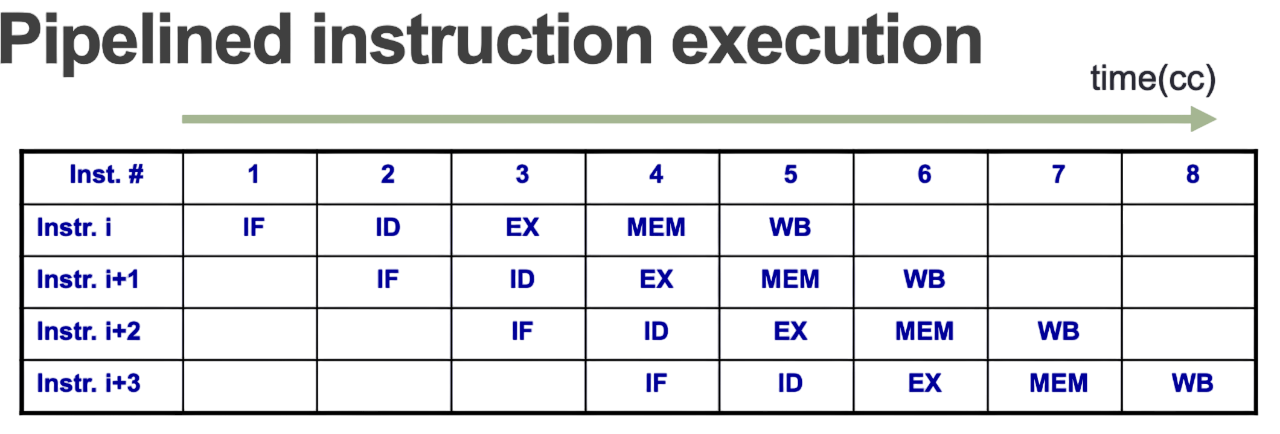

5 stages

- IF: Instruction Fetch

- ID: Instruction decode & registers read

- EX: Execute operation ro calculate address

- MEM: access memory

- WB: write back to registers

General Idea

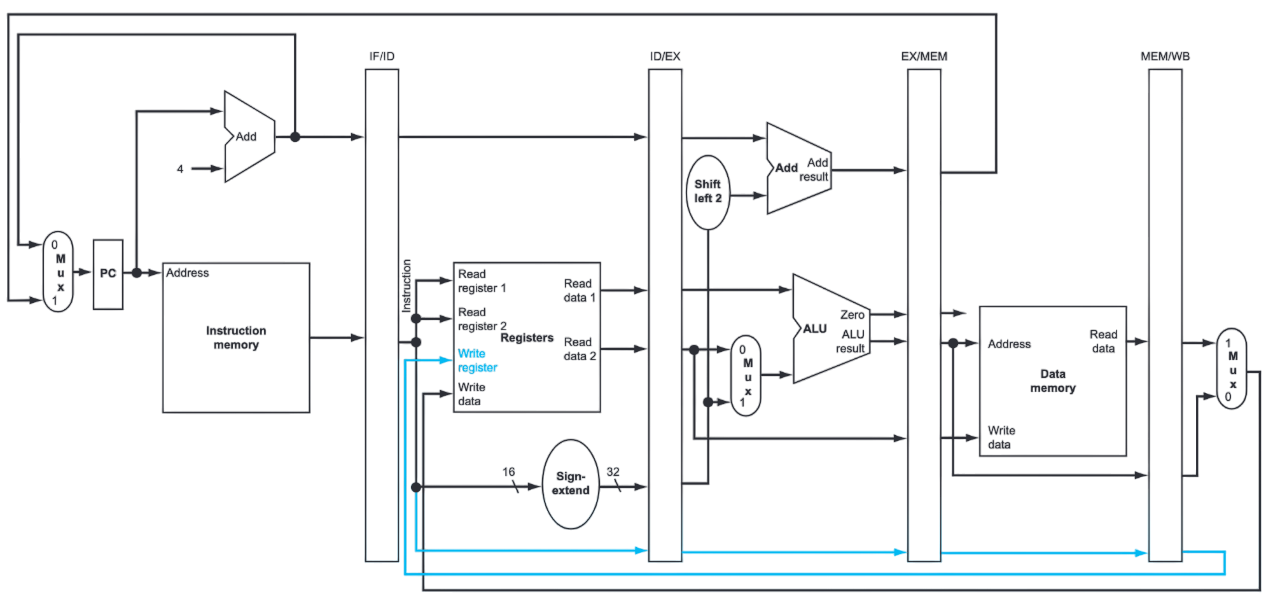

Partition the single cycle datapath into sections. Each section forms a pipeline stage

Try to make data flow in the same direction(main on write back and pc update operation)

registers

The registers inserted between the pipeline stages are called pipeline stage register, or simply pipeline register

Each pipeline register is named after the two stages separated by that register

All instructions advance from one stage to the next stage in one clock cycle.

Datapath Design

Why Write register signal is changed? Yes, if we stick on previous design, the signal represent the register which should be written in next a few(3 exactly) instructions.(Remember, now the all the component is working in parallel)

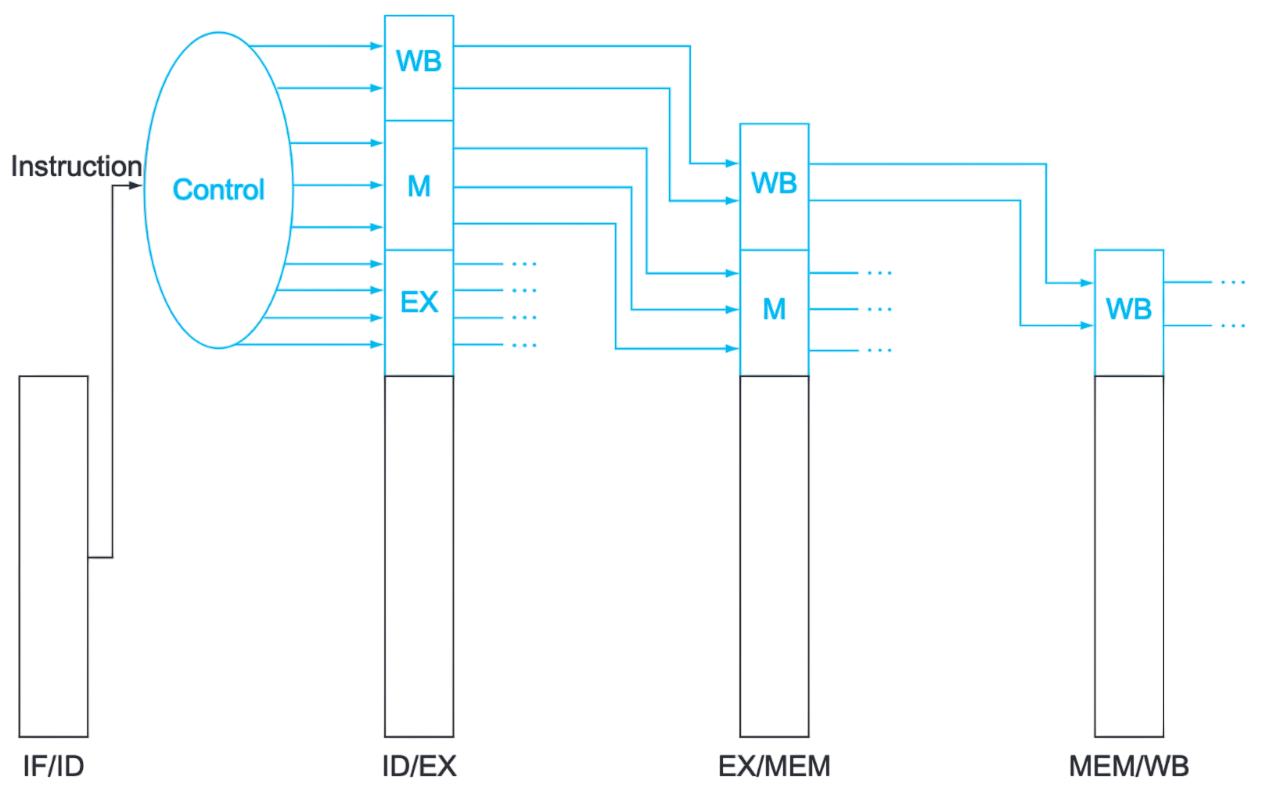

Control Unit

Pipeline is used in dataPath design. Then in each stage, control unit should output it corresponding signal. A smart design is that control units output all the required signal in ID stage and save all of them to stage register. In each stage, data path get required signal Hierarchically.

Hazards

Pipeline hazards are the situations where instruction execution cannot proceed in the pipeline.

- Structural hazard

- Data hazard

- Control hazard

Mainly due to something required is currently not available.

Structural hazard

A structural hazard occurs when one resource is to be used by more than one instruction in one clock cycle.

Solutions: Never access a resource more than once per clock cycle

- Allocate each resource to a single pipeline stage.

- Every instruction must follow the same execution stage sequence

Data hazard

Data hazards are caused by data dependency

Four kinds of data hazard

- RAR

- WAW

- RAW

- WAR

A basic solution is stalling pipeline. which is just wait.

Another one is forwarding. In some cases, circuit can “detect” the data hazard and get the value from previous instruction “middle register”.

Source register data of the instruction in the Ex stage is dependent on the destination register data of its preceding instruction in the MEM stage

Source register data of the instruction in the Ex stage is dependent on the destination register data of its preceding instruction in the WB stage

control hazard

branch prediction

- static prediction

Misprediction lead to pipeline flush.(3 instructions has been wasted).

We can calculate the target address in ID stage. check conition in ID stage(use XOR to compare the register contents).Require forwarding to ID stage and hazard detection. - dynamic prediction

The history is stored in a table, called branch history table or branch prediction table. - third